На проходящей в эти дни конференции IEDM 2023 компания Intel сообщила о ряде достижений, которые продлят работу закона Мура. Плотность транзисторов на единицу площади продолжит увеличиваться прежними или близкими к прежним темпами, обещая дойти к 2030 году до триллиона транзисторов в одном процессоре.

Рекламное представление CFET (комплементарных полевых транзисторов). Источник изображения: Intel

Ещё в мае стало известно, что Intel намерена внедрить в одном из будущих поколений процессоров многоуровневую компоновку транзисторов. Речь идёт о вертикальном расположении комплементарных полевых транзисторов (CFET). На конференции представитель компании сообщил, что это будут первые в индустрии решения такого рода, шаг затвора которых составит до 60 нм. Сейчас такие транзисторы изготавливаются с расположением бок о бок в горизонтальной плоскости, тогда как в ближайшие годы компания начнёт производить их один над другим в сочетании с горизонтальными полностью окружёнными затворами каналами. Это значительно увеличит плотность размещения транзисторов на кристалле, что также потребует сигнального доступа к транзисторам с обратной стороны подложки.

Но сначала Intel введёт в обиход новый (и первый за 13 лет в её практике) транзистор. Компания называет его RibbonFET Gate-All-Around (GAA). Каналы у такого транзистора будут в виде тонких горизонтально ориентированных наностраниц, расположенных друг над другом. Канала будет четыре, и все они будут полностью окружены одним затвором. Начало производства транзисторов RibbonFET запланировано на первую половину 2024 года. Вертикальная компоновка из комплементарных пар таких транзисторов, очевидно, произойдёт на несколько лет позже. Вероятно в одном и том же техпроцессе удвоения количества транзисторов не произойдёт. Однако можно ожидать роста плотности транзисторов до 30 % или около того, что в сочетании с переходом на ещё более тонкие техпроцессы позволит следовать закону Мура.

Близкое к реальному представление пары вертикально расположенных друг над другом комплементарных транзисторов

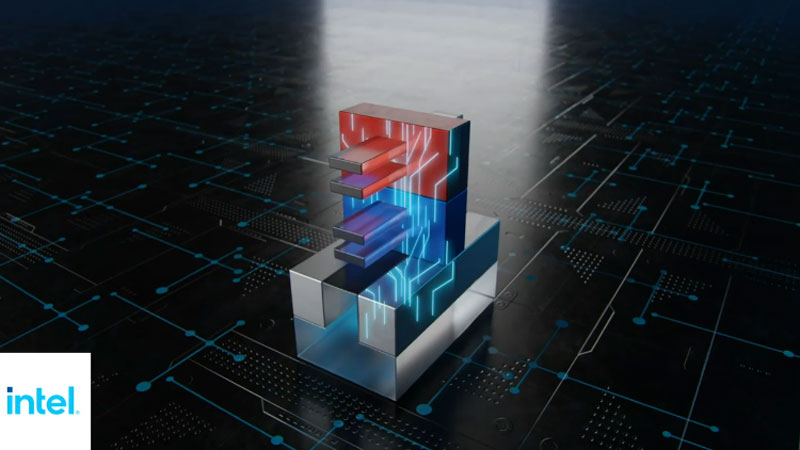

Также на конференции Intel сообщила о других достижениях. В частности, она рассказала о выпуске кристаллов с питанием транзисторов через обратную сторону подложки. Это разгрузит сторону с сигнальными линиями, что позволит поднять тактовую частоту и увеличить мощность питания, поскольку последним будет предоставлено больше пространства для проводников и, следовательно, откроет простор для изготовления подводящих питание линий с большим сечением. Правда, когда придёт черёд вертикально расположенных транзисторов, через заднюю подложку будут предусмотрены также прямые сигнальные контакты, что поможет разгрузить основную сигнальную инфраструктуру.

Обычное горизонтальное расположение транзисторов с наностраничными каналами

Также компания сообщила об опыте изготовления на единой кремниевой подложке в дополнение к обычным транзисторам транзисторов из нитрида галлия (GaN). Технология показала свою жизнеспособность и позволит в будущем на 300-мм кремниевых подложках выпускать силовую электронику или электронику с силовыми элементами с использованием нитрида галлия. Сегодня такие элементы выпускаются на своих подложках (и это обычно не кремний) и интегрируются с кремниевой электроникой на уровне сборок.

Разделение питания и сигнального интерфейса по разное стороны от кристалла (на прямую и тыловую стороны)

Наконец, Intel сообщила об успешном движении в направление «двумерных» транзисторов с 2D-каналами. Материалы для 2D-каналов на основе дихалькогенида переходных металлов (TMD) предоставляют уникальную возможность масштабирования физического затвора транзистора длиной менее 10 нм. На IEDM 2023 Intel показала прототипы высокомобильных TMD-транзисторов как для NMOS (n-канальный металлооксидный полупроводник), так и для PMOS (p-канальный металлооксидный полупроводник).

Также компания представила первый в мире gate-all-around (GAA) 2D TMD PMOS-транзистор и первый в мире 2D PMOS-транзистор, изготовленный на 300-миллиметровой пластине. Ждём более подробных докладов, которые помогут ознакомиться с этими новшествами.