Компания IBM анонсировала новое поколение вычислительных систем для искусственного интеллекта — процессор Telum II и ускоритель IBM Spyre. Оба продукта предназначены для ускорения ИИ и улучшения производительности корпоративных приложений. Telum II предлагает значительные улучшения благодаря увеличенной кеш-памяти и высокопроизводительным ядрам. Ускоритель Spyre дополняет его, обеспечивая ещё более высокие показатели для приложений на основе ИИ.

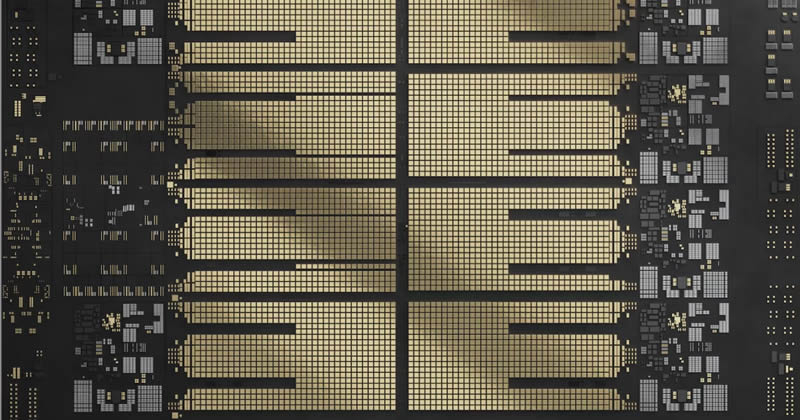

Источник изображения: IBM

Как сообщается в блоге компании, новый процессор IBM Telum II, разработанный с использованием 5-нанометровой технологии Samsung, будет оснащён восемью высокопроизводительными ядрами, работающими на частоте 5,5 ГГц. Объём кеш-памяти на кристалле получил увеличение на 40 %, при этом виртуальный L3-кеш вырос до 360 Мбайт, а L4-кеш до 2,88 Гбайт. Ещё одним нововведением является интегрированный блок обработки данных (DPU) для ускорения операций ввода-вывода и следующее поколение встроенного ускорителя ИИ.

Telum II предлагает значительные улучшения производительности по сравнению с предыдущими поколениями. Встроенный ИИ-ускоритель обеспечивает в четыре раза большую вычислительную мощность, достигая 24 триллионов операций в секунду (TOPS). Архитектура ускорителя оптимизирована для работы с большими языковыми моделями и поддерживает широкий спектр ИИ-моделей для комплексного анализа структурированных и текстовых данных. Кроме того, новый процессор поддерживает тип данных INT8 для повышения эффективности вычислений. При этом на системном уровне Telum II позволяет каждому ядру процессора получать доступ к любому из восьми ИИ-ускорителей в рамках одного модуля, обеспечивая более эффективное распределение нагрузки и достигая общей производительности в 192 TOPS.

IBM также представила ускоритель Spyre, разработанный совместно с IBM Research и IBM Infrastructure development. Spyre оснащён 32 ядрами ускорителя ИИ, архитектура которых схожа с архитектурой ускорителя, интегрированного в чип Telum II. Возможность подключения нескольких ускорителей Spyre к подсистеме ввода-вывода IBM Z через PCIe позволяет существенно увеличить доступные ресурсы для ускорения задач искусственного интеллекта.

Telum II и Spyre разработаны для поддержки широкого спектра сценариев использования ИИ, включая метод ensemble AI. Этот метод использует преимущества одновременного использования нескольких ИИ-моделей для повышения общей производительности и точности прогнозирования. Примером может служить обнаружение мошенничества со страховыми выплатами, где традиционные нейронные сети успешно сочетаются с большими языковыми моделями для повышения эффективности анализа.

Оба продукта были представлены 26 августа на конференции Hot Chips 2024 в Пало-Альто (Калифорния, США). Их выпуск планируется в 2025 году.